台积电展示硅光子先进封装平台 入局cpo-九游会旧版

光纤在线编辑部 2024-02-22 17:38:53 文章来源:原文转载

导读:台积电入局硅光子技术平台。

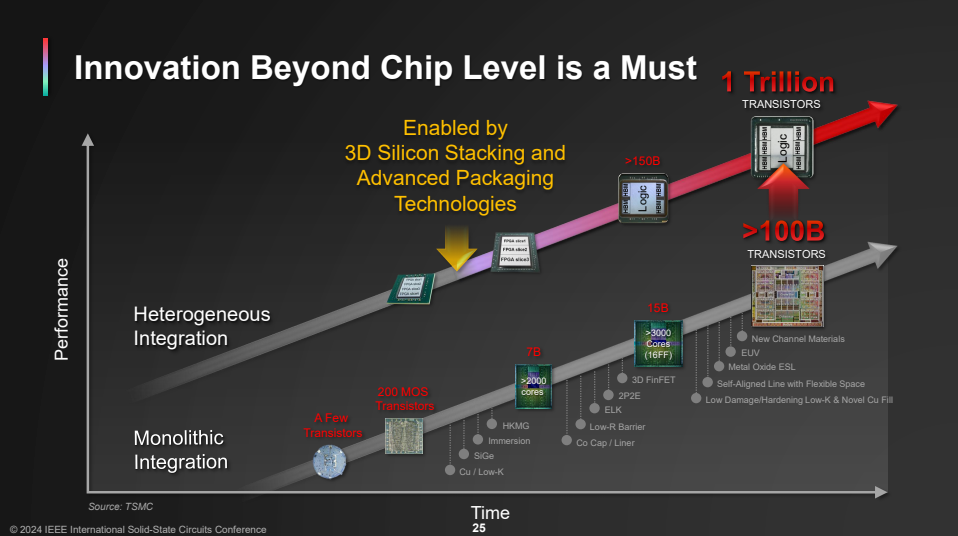

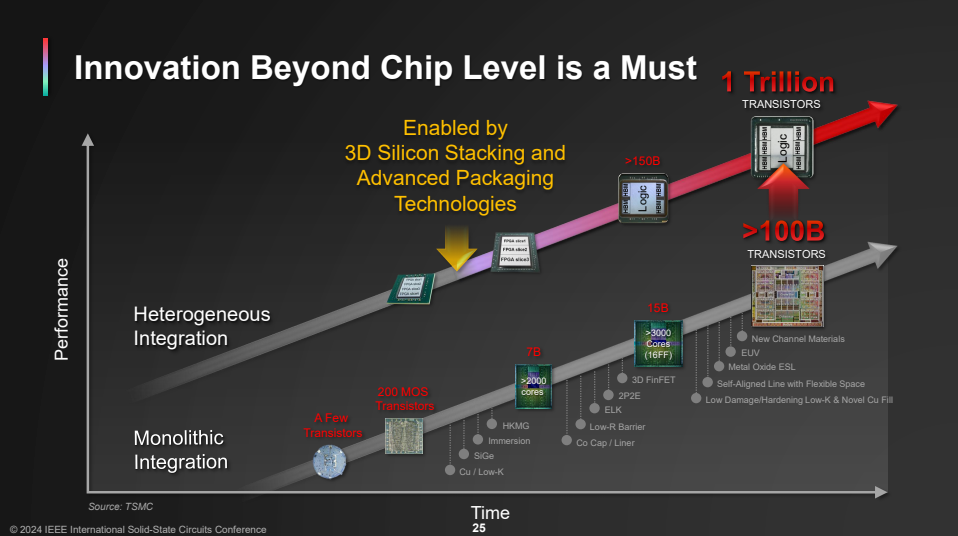

2/22/2024,光纤在线讯,近日在国际固态电路大会(isscc 2024)上,台积电正式公布了其用于高性能计算 (hpc)、人工智能芯片的全新封装平台,该技术有望将芯片的晶体管数量从目前的1000亿提升到1万亿。

台积电业务开发资深副总裁张晓强 (kevin zhang) 在演讲中表示,开发这项技术是为了提高人工智能芯片的性能。要想增加更多的hbm高带宽存储器和chiplet架构的小芯片,就必须增加更多的组件和ic基板,这可能会导致连接和能耗方面的问题。

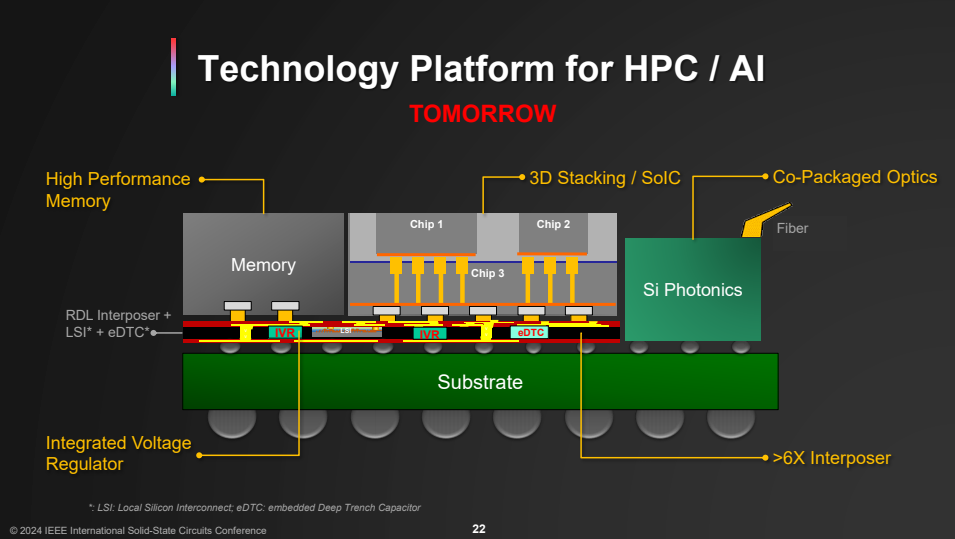

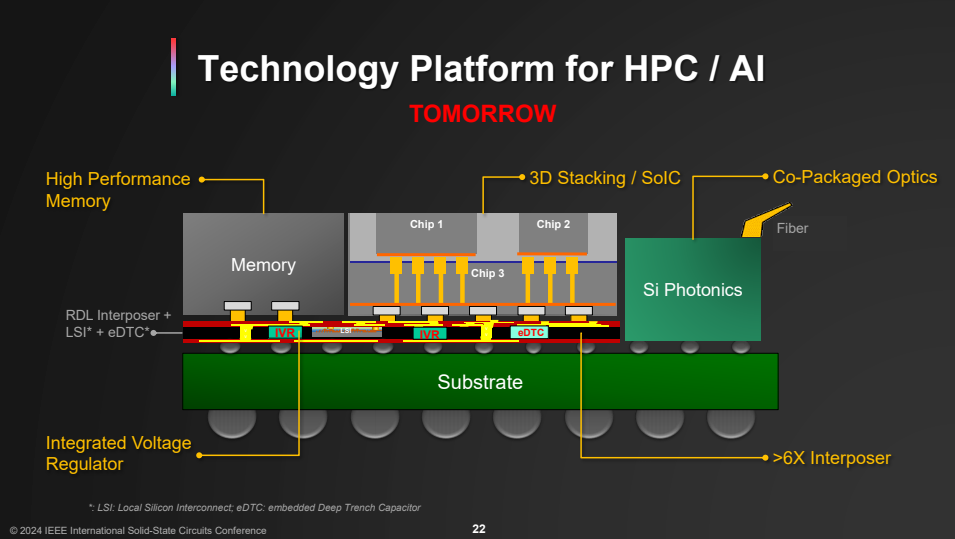

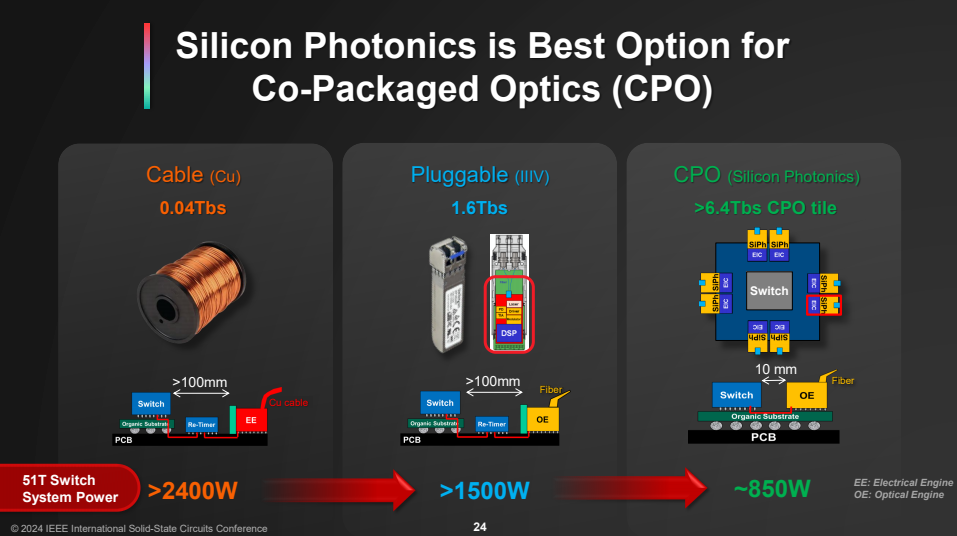

张晓强强调,台积电的新封装技术通过硅光子技术,使用光纤替代传统i/o电路传输数据。而另一大特点是,使用异质芯片堆栈在ic基板上,采用混合键合来最大化i/o,这也使得运算芯片和hbm高带宽存储器可以安装在硅中介层上。他还表示,这一封装技术将采用集成稳压器来处理供电的问题。

台积电并未透露新一代封装技术的具体商业化时间。

但值得注意的是,去年以来,台积电已频频传出布局硅光及cpo的动向。

2023年9月曾有消息称,台积电正与博通、英伟达等大客户联手开发硅光及cpo光学元件等新品,最快2024年下半年开始迎来大单,2025年有望迈入放量产出阶段。

彼时业内人士透露,台积电未来有望将硅光技术导入cpu、gpu等运算制程当中,内部的电子传输线路更改为光传输,计算能力将是现有处理器的数十倍起跳。

而台积电副总裁之前曾公开表示,如果能提供一个良好的“硅光整合系统”,就能解决能耗与ai运算能力两大关键问题,“这会是一个新的典范转移。我们可能处于一个新时代的开端。”

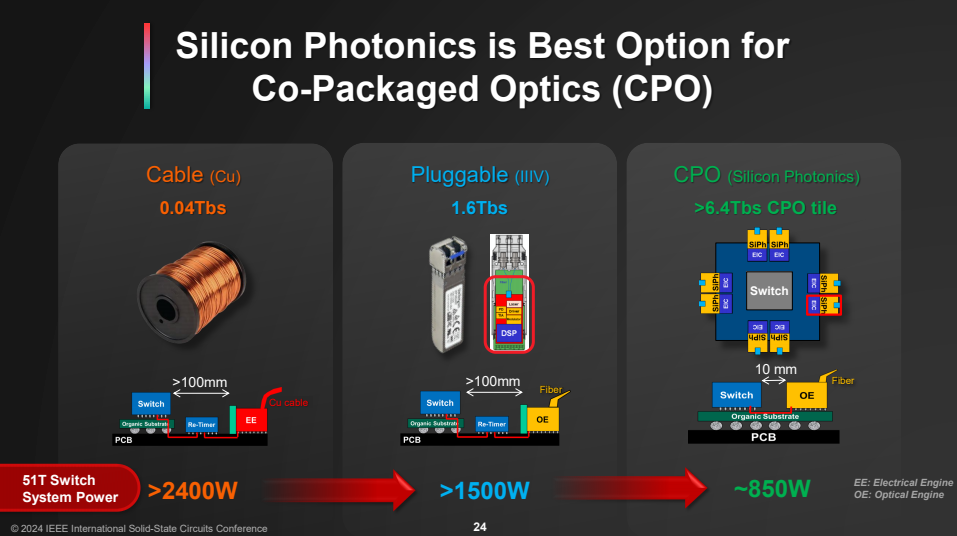

业内分析称,高速资料传输目前仍采用可插拔光学元件,随着传输速度快速进展并进入800g时代、未来更将迎来1.6t至3.2t等更高传输速率,功率损耗及散热管理问题将会是最大难题。而半导体业界推出的九游会旧版的解决方案,便是将硅光子光学元件及交换器asic,通过cpo封装技术整合为单一模组,此方案已开始获得微软、meta等大厂认证并采用在新一代网路架构。

台积电业务开发资深副总裁张晓强 (kevin zhang) 在演讲中表示,开发这项技术是为了提高人工智能芯片的性能。要想增加更多的hbm高带宽存储器和chiplet架构的小芯片,就必须增加更多的组件和ic基板,这可能会导致连接和能耗方面的问题。

张晓强强调,台积电的新封装技术通过硅光子技术,使用光纤替代传统i/o电路传输数据。而另一大特点是,使用异质芯片堆栈在ic基板上,采用混合键合来最大化i/o,这也使得运算芯片和hbm高带宽存储器可以安装在硅中介层上。他还表示,这一封装技术将采用集成稳压器来处理供电的问题。

台积电并未透露新一代封装技术的具体商业化时间。

但值得注意的是,去年以来,台积电已频频传出布局硅光及cpo的动向。

2023年9月曾有消息称,台积电正与博通、英伟达等大客户联手开发硅光及cpo光学元件等新品,最快2024年下半年开始迎来大单,2025年有望迈入放量产出阶段。

彼时业内人士透露,台积电未来有望将硅光技术导入cpu、gpu等运算制程当中,内部的电子传输线路更改为光传输,计算能力将是现有处理器的数十倍起跳。

而台积电副总裁之前曾公开表示,如果能提供一个良好的“硅光整合系统”,就能解决能耗与ai运算能力两大关键问题,“这会是一个新的典范转移。我们可能处于一个新时代的开端。”

业内分析称,高速资料传输目前仍采用可插拔光学元件,随着传输速度快速进展并进入800g时代、未来更将迎来1.6t至3.2t等更高传输速率,功率损耗及散热管理问题将会是最大难题。而半导体业界推出的九游会旧版的解决方案,便是将硅光子光学元件及交换器asic,通过cpo封装技术整合为单一模组,此方案已开始获得微软、meta等大厂认证并采用在新一代网路架构。

关键字: 硅光

光纤在线公众号

更多猛料!欢迎扫描左方二维码关注光纤在线官方微信更多关于 硅光 的新闻

- roel beats谈硅光在非通信市场的机会与挑战 (02-20)

- (02-06)

- (02-02)

- (01-12)

- (01-05)

- (01-04)

- 上海工研院2024年硅光mpw排期发布,欢迎预定流片! (01-03)

- (12-29)

- (12-12)

- (12-07)

相关产品

热门搜索

热门新闻

最新简历

- 阳江 副总经理/副总裁品保经理/主管营运经理/主管

- 衡阳 请选择职位

- 深圳 副总经理/副总裁研发部经理项目经理/主管

- 淮安 项目经理/主管技术/工艺设计工程师九游会官网登录入口网页的技术支持工程师

- 深圳 生产/工程技术类全部生产/工程技术类全部生产/工程技术类全部